近日公司低维半导体材料设计与器件模拟团队与香港城市大学合作,在传统三维金属与二维半导体异质结界面势垒起源及调控机制研究方面取得新进展,相关成果以“Resolving Interface Barrier Deviation from the Schottky-Mott Rule: A Mitigation Strategy via Engineering MoS2-Metal van der Waals Contact”为题发表在自然指数期刊《J. Phys. Chem. Lett.》 (2023, 14, 2940-2949)上。

传统金属与二维半导体构成的异质结是现代电子、光电子和自旋电子器件的重要组成部分,其中界面接触电阻主要由界面肖特基势垒决定。按照肖特基-莫特定则,界面肖特基势垒由金属与半导体的能带对齐关系决定,选择合适功函数的金属构造异质结,可以消除肖特基势垒,实现欧姆接触。然而,在半导体表面蒸镀金属薄膜产生的界面无序会诱导费米能级钉扎效应,导致很难根据肖特基-莫特定则理性设计和调控界面势垒。最近Manish Chhowalla等人(Nature 2019)和Myung-Ho Bae等人(npj 2D Mater. Appl. 2021)分别采用低温电子束蒸发方法在少层二硫化钼表面蒸镀金属铟薄膜,成功实现有序的无缺陷的范德华接触,获得低的界面接触电阻。研究者进一步在金属铟背面镀金或钯形成合金层,能明显调控界面接触电阻。结果分析表明,铟与二流化钼界面低电阻归于界面接触诱导的能态的贡献,其能带对齐依然严重偏离肖特基-莫特定则预测值即肖特基势垒极限值。尽管两个实验组实现了铟与二流化钼有序的范德华接触,但是界面势垒偏离肖特基-莫特定则预测的结果的本质原因仍不清楚,特别是对蒸镀金或钯形成合金层对肖特基势垒的调控机制的理解仍存在争议。

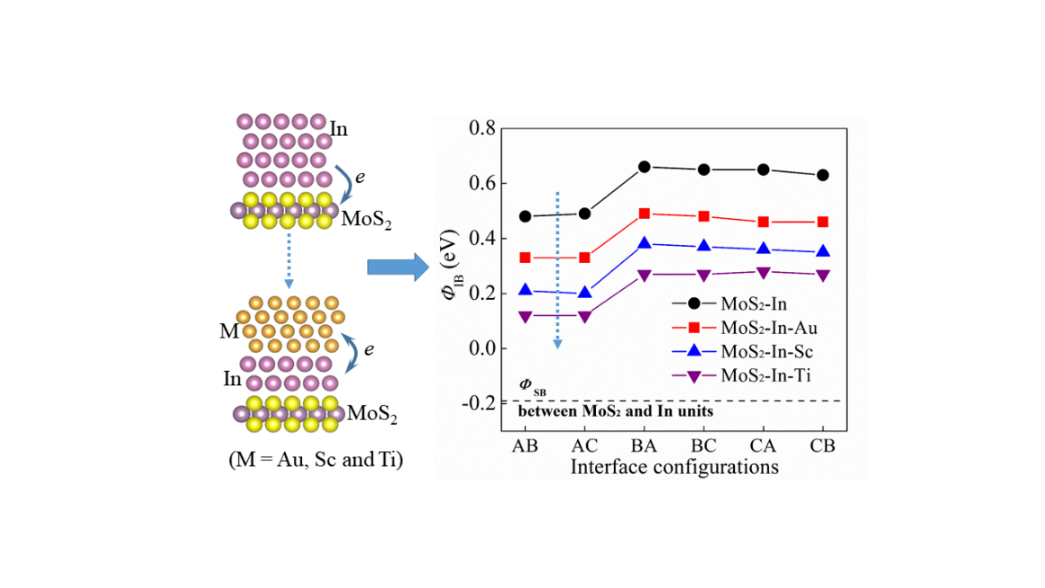

图1. 铟/二流化钼异质结模型以及界面肖特基势垒随界面构型与合金层种类的变化。

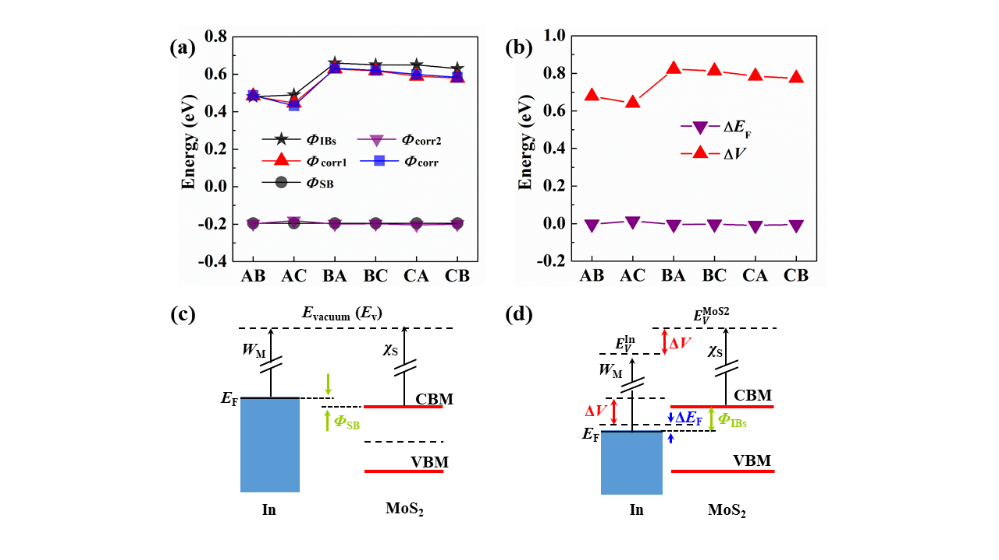

界面肖特基势垒的形成与复杂的界面相互作用密切相关,两者通常会随界面堆叠构型的改变而变化。为此,本工作基于第一性原理计算方法,首先,构造铟与二流化钼异质结的六种界面堆叠构型,计算其电子结构,揭示界面相互作用与肖特基势垒对界面构型的依赖性。结果表明,对于六种界面构型,获得的静电势差、偶极矩和费米能级移动等界面相互作用与从能带结构获得的界面肖特基势垒随界面构型表现出相似的变化趋势,其中界面肖特基势垒值的变化范围为0.48至0.66 eV,明显偏离肖特基势垒的极限值-0.19 eV。其次,进一步考虑界面相互作用对界面势垒的修正,本工作发现在肖特基势垒极限值的基础上考虑界面静电势差(ΔV)和费米能级移动(ΔEF)的修正值与界面肖特基势垒值复合得很好,表明肖特势垒偏离肖特基极限值的原因是界面静电势差和费米能级移动的综合效应。最后,本工作在铟/二流化钼异质结的金属铟的背面引进金、钪或钛薄膜,可以有效减小界面肖特基势垒以及静电势差与费米能级移动的和(ΔEF+ΔV)。更重要的是,引进钛薄膜使界面肖特基势垒降低到0.12 eV,明显小于引进金薄膜获得的界面肖特基势垒值(0.30 eV)。因此,金属铟背面引进钛涂层可以显著降低界面接触电阻。进一步分析表明,引进合金对界面肖特基势垒的调控与两类合金层的电负性与功函数的相对值密切相关。本工作基于此提出理性调控传统三维金属与二维半导体异质结界面肖特基势垒的方法。

图2. 界面肖特基势垒、静电势差和费米能级移动随界面堆叠构型的变化。

低维半导体材料设计与器件模拟团队李中军教授为论文第一作者,吴玉程教授和香港城市大学曾晓成教授为论文共同通讯作者。本工作得到了国家重点研发计划和国家自然科学基金等项目的资助。

文章链接:https://pubs.acs.org/doi/10.1021/acs.jpclett.3c00056?ref=pdf

文/李中军 图/汪海迪 审核/高伟清